# OPERATIONS MANUAL PCM-AIO

**NOTE:** This manual has been designed and created for use as part of the WinSystems' Technical Manuals CD and/or the WinSystems' website. If this manual or any portion of the manual is downloaded, copied or emailed, the links to additional information (i.e. software, cable drawings) will be inoperable.

WinSystems reserves the right to make changes in the circuitry and specifications at any time without notice. ©Copyright 1993 by WinSystems. All Rights Reserved.

## **REVISION HISTORY**

## P/N 403-0172-000

| ECO NUMBER | Date Code | Rev Level |

|------------|-----------|-----------|

| ORIGINATED | 032993    | Α         |

| 93-67      | 092493    | A1        |

| 94-31      | 940817    | A2        |

| 98-29      | 980414    | A3        |

| 98-48      | 980723    | В         |

# **TABLE OF CONTENTS**

| Section | Paragraph Title                            | Page |

|---------|--------------------------------------------|------|

|         | Visual Index- Quick Reference              | i    |

| 1       | General Information                        | 1-1  |

| 1.1     | Features                                   | 1-1  |

| 1.2     | General Description                        | 1-1  |

| 1.3     | Specifications                             | 1-3  |

| 2       | PCM-AIO Technical Reference                | 2-1  |

| 2.1     | Introduction                               | 2-1  |

| 2.2     | I/O Addressing Selection                   | 2-1  |

| 2.3     | A/D Registers                              | 2-2  |

| 2.4     | D/A Registers                              | 2-2  |

| 2.5     | Interrupt Routing Selection                | 2-3  |

| 2.6     | A/D In put Connector                       | 2-3  |

| 2.7     | Single Ended Operation                     | 2-3  |

| 2.8     | Differential Operation                     | 2-3  |

| 2.9     | Unipolar/Bipolar Operation                 | 2-4  |

| 2.10    | A/D Software Interface                     | 2-4  |

| 2.11    | A/D Calibration Procedure                  | 2-5  |

| 2.12    | Output Coding                              | 2-6  |

| 2.13    | A/D Software Examples                      | 2-6  |

| 2.14    | D/A Output Connector                       | 2-10 |

| 2.15    | D/A Voltage Reference and Output Selection | 2-10 |

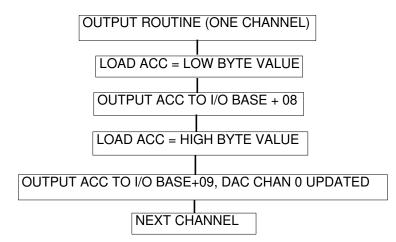

| 2.16    | D/A Software Flowchart/Assembly Routine    | 2-10 |

| 2.17    | D/A Calibration Procedure                  | 2-12 |

|         |                                            |      |

APPENDIX A MAX 180 Datasheet Reprint APPENDIX B Cable Drawings and Software

Warranty and Repair Information

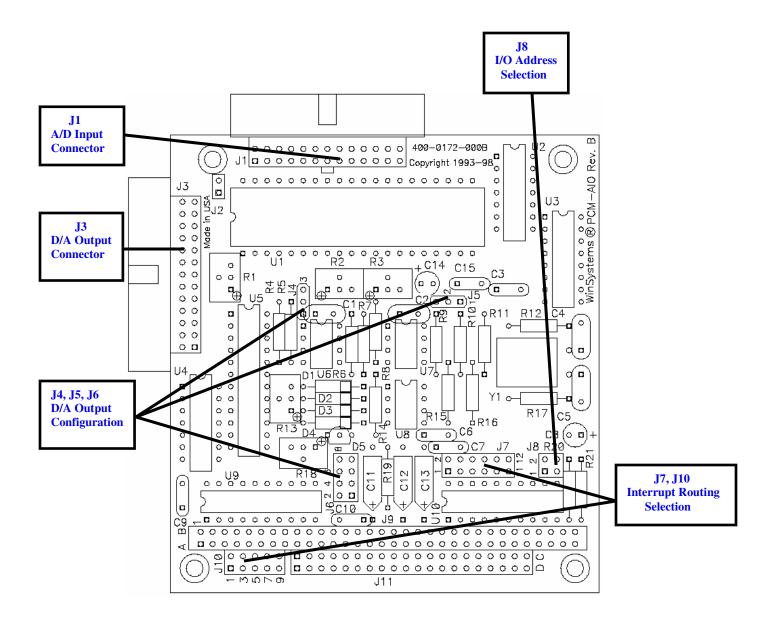

# Visual Index – Quick Reference

For the convenience of the user, a copy of the Visual Index has been provided with direct links to connector and jumper configuration data.

# **1** GENERAL INFORMATION

# 1.1 FEATURES

- Low cost, 12-bit A/D

- Up to 8 A/D input channels

- Each A/D channel configurable for Unipolar (0 to +5V) or Bipolar (-2.5 to +2.5V)

- Single-ended or Differential Input Modes

- Built-in Sample-and-Hold

- 100KHz sampling rate

- I/O mapped on the PC/104 Bus

- Processor independent

- Very low power, all CMOS components

- Two channel 12 Bit CMOS D/A converter

- Selectable UNIPOLAR or BIPOLAR voltage output for each channel

- Two output voltage ranges: 0 to 5V or -5V to +5V

## **1.2 GENERAL DESCRIPTION**

## 1.2.1 PC/104 Bus Interface

The PCM-AIO is I/O port mapped with the unique port address determined by an on board EPAL decoder. The PCM-AIO uses a total of 8 I/O ports and is designed to work with standard NMOS/TTL or CMOS base boards.

## 1.2.2 Analog to Digital Converter

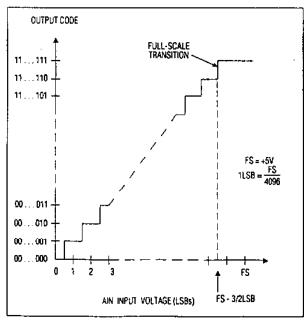

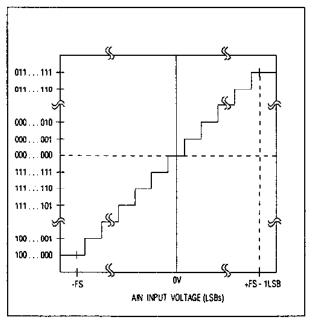

The PCM-AIO contains the Maxim MAX180, 12-bit data acquisition system. It combines an 8 channel input multiplexer, high bandwidth Track-and-Hold (T/H), low-drift zener reference, and flexible microprocessor interface with a high conversion speed, successive approximation analog to digital converter. The device samples and digitizes at a 100KHz throughput rate. The MAX180 can be software configured for unipolar or bipolar conversions and single-ended or differential inputs on a per channel basis. Output coding is natural binary for unipolar operation with 1 LSB = 1.22mV (5V/4096). Coding is twos complement for bipolar. Potentiometers are on the card to permit both gain and offset adjustment.

## 1.2.3 Starting an A/D conversion

The conversion is begun by writing a word to the control register to select the channel and specify if it is single-ended/differential and unipolar/bipolar. Output data is latched and the PCM-AIO signals the base board that conversion is complete and data is available. This board sets a Busy flag for use in a polled mode and can generate an interrupt after each completed conversion.

## 1.2.4 A/D Input Configuration

All input channel are wired to J1, a 26-pin right angle male connector. It has the same pin-out as WinSystems' MCM/LPM-A/D12. J1 is configured so that mass termination type flat ribbon cable or discreet wires can be connected to it. WinSystems offers the CBL-120-3 which is a 3 foot, # 28 AWG, ribbon cable designed to provide access to signals from the 26-pin, 0.100 " grid connector on the PCM-AIO board. One end of the cable has a polarized, 26-pin female socket connector with strain relief that plugs into the board and the other end is open to allow users to make their own custom termination. The CBL-130-4 is a 4 foot, ribbon cable that will connect the PCM-AIO to the Analog-ADP. This board is a non-isolated signal conditioner and termination panel.

## 1.2.5 Digital to Analog Converter

The PCM-AIO has two 12 bit digital to analog convertor channels. Each channel can be configured for either a unipolar or bipolar output with one of two output ranges: 0 to 5V or + /-5V. The D/A section on the PCM-AIO takes 4 I/O ports.

## 1.2.6 DA Operation

Each D/A channel on the PCM-AIO is reset to logic zero after a system reset. To output a digital word to a channel, the low byte is written to the low byte address (ALWAYS EVEN), the upper 4 bits of the 12 bit word is written to the next address (ALWAYS ODD). After writing the upper 4 bits, the channel is automatically updated. It is important to note that a channel is only updated when the upper 4 bits are written to the odd address.

EXAMPLE: 0 to 5V unipolar output selected D/A Ports are located at 100-10B

To Output 800 HEX to channel 0 (should equal 2.5V output)

1. OutpuT 00 HEX TO I/O PORT 108 HEX 2. Output 08 HEX TO I/O PORT 109 HEX

When the 08 hex is written to I/O Port 101, the 12 bit word will be converted to a 2.5V output.

## 1.2.7 PC/104 Module

PC/104 multimodule boards are small (3.550" x 3.775"), I/O or memory mapped boards which plug into a base board. The PC/104 boards connect to the PC/104 bus connector and convert the PC/104 bus signals to a defined memory or I/O interface. The PC/104 is a unique design approach to Embedded Systems users offering a broad range of expansion boards joined together on the PC/104 interface. The PCM-AIO is designed to fit on all Win-Systems' processors that have PC/104 connectors, our LPM/MCM-SX386/486, and other CPU base boards.

# **1.3 SPECIFICATIONS**

## 1.3.1 Electrical

<u>A/D</u>

| Number of Channels: | Up to 8                                                     |

|---------------------|-------------------------------------------------------------|

| A/D Resolution:     | 12-bits                                                     |

| Input range:        | 0 to +5 volts; single-ended -2.5 to +2.5 volts; differetial |

| Coding:             | Natural binary (unipolar)                                   |

|                     | Two's complement (bipolar)                                  |

| Nonlinearity:       | 1 LSB                                                       |

| Gain error:         | Adjustable to zero                                          |

| Conversion speed:   | 10 microseconds                                             |

|                     |                                                             |

## <u>D/A</u>

| Number of Channels: | 2                          |

|---------------------|----------------------------|

| D/A Resolution:     | 12-bits                    |

| Voltage Output:     | 0 to 5 VDC or -5 to +5 VDC |

| Output Drive:       | 2.5 mA                     |

|                     |                            |

## **Power Requirements:**

| VCC  | +5 VDC 5% at 35 mA (typ. outputs unloaded)  |

|------|---------------------------------------------|

| VCC1 | -12VDC 10% at 15 mA (typ. outputs unloaded) |

| VCC2 | +12VDC 10% at 15 mA (typ. outputs unloaded) |

## 1.3.2 Mechanical

Dimensions:

3.550" x 3.775"

Connectors :

A/D Input:

26-pin dual pin on 0.100"

D/A Output:

26-pin dual pin on 0.100"

PC/104:

62-pin dual pin on 0.100"

## 1.3.3 Environmental

Operational Temperature: 0° C to +65° C

## 1.3.4 Ordering Information

| PCM-AIO   | 12-bit A/D converter                                     |

|-----------|----------------------------------------------------------|

| CBL-120-3 | 3 ft., 26 conductor ribbon cable unterminated            |

| CBL-130-4 | 4 ft., 26 conductor, ribbon cable to the Analog-ADP card |

|           | Analog-ADP Analog termination panel                      |

# 2 PCM-AIO Technical Reference

## 2.1 Introduction

This section of the manual is intended to provide sufficent information regarding the configuration, and programming of the PCM-AIO module. A complete reprint of the MAX 180 datasheet is provided in Appendix C for specific information on the chip. Questions not adequately addressed in this section should be addressed to the WinSystems Technical Support department at (817) 274-7553 between 8AM and 5PM Central time Monday through Friday.

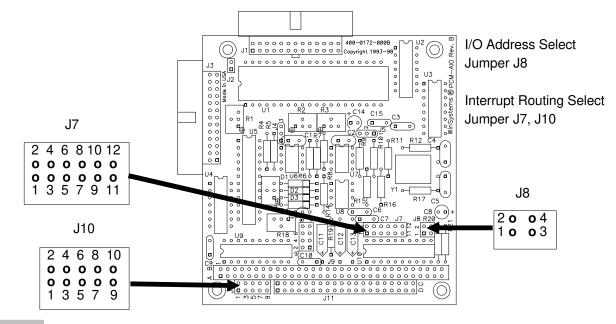

## 2.2 I/O Address Select

The PCM-AIO decodes 16 I/O ports to access the board. The I/O port addresses are determined by an EPAL and is controlled by jumper block J8. The figures below show the Base I/O address as determined by the jumpering of J8.

# 2.3 A/D Registers

## **OFFSET 0 - Write**

| Bits 7-5 | Unused                                         |

|----------|------------------------------------------------|

| Bit 4    | 1 = Differential Input, 0 = Single Ended input |

| Bit 3    | 1 = Bipolar Input, 0 = Unipolar Input          |

| Bits 2-0 | Channel Select 0 to 7                          |

## **OFFSET 0 - Read**

Bits 7-0 LSB of converted data

## OFFSET 1 - Read

| Bits 7-4 | Unused                         |

|----------|--------------------------------|

| Bits 3-0 | Upper 4 Bits of converted data |

## **OFFSET 4 - Read**

| Bit 7    | 1 = A/D Busy, $0 =$ Conversion complete |

|----------|-----------------------------------------|

| Bits 6-0 | Unused                                  |

# 2.4 D/A Registers

## OFFSET 8 - Write

## OFFSET 9 - Write

| Bits 7-4 | Unused                                          |

|----------|-------------------------------------------------|

| Bits 3-0 | Channel A - Upper 4 bits of 12-Bit ouput value. |

## OFFSET 10 - Write

Bits 7-0 Channel B LSB data

## OFFSET 11 - Write

| Bits 7-4 | Unused                                          |

|----------|-------------------------------------------------|

| Bits 3-0 | Channel B - Upper 4 bits of 12-Bit ouput value. |

# 2.5 Interrupt Routing Select

The PCM-AIO is capable of generating an interrupt on conversion complete from the MAX180. This interrupt may be routed to any of several PC/104 bus interrupts using the jumper block at J7 or J10. The jumpering detail for J7 and J10 is shown here :

| J7                                                          | _                                             | J10                                                                                                                                  |

|-------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1 o o2<br>3 o o4<br>5 o o6<br>7 o o8<br>9 o o10<br>11 o o12 | IRQ2<br>IRQ7<br>IRQ6<br>IRQ5<br>IIRQ4<br>IRQ3 | 1 o o 2       IRQ14         3 o o 4       IRQ15         5 o o 6       IRQ12         7 o o 8       IRQ11         9 o o 10       IRQ10 |

## 2.6 A/D Input Connector

The figure below shows the pinout for the PCM-AIO analog input connector J1 in both single-ended and differential modes.

| J1                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Channel 0<br>Channel 2<br>Ground<br>Channel 4<br>Ground<br>Channel 6<br>Ground<br>Channel 1<br>Ground<br>Channel 3<br>Ground<br>Channel 5<br>Channel 7 | 2       0       0       15         3       0       0       16         4       0       0       17         5       0       0       18         6       0       0       19         7       0       20       8       0       21         9       0       0       22       3       10       0       23         1       1       0       0       25       12       0       25 | Channel 1<br>Channel 3<br>Ground<br>Channel 5<br>Ground<br>Channel 7<br>Ground<br>N/C<br>Ground<br>N/C<br>Ground<br>N/C<br>Ground<br>N/C |  |  |  |

J1 Input Pin Definitions - Single Ended Mode

|                                                                                                                                                                                        | J                        | 1                                                                                            |                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel 0 (+)<br>Channel 2 (+)<br>Ground<br>Channel 4 (+)<br>Ground<br>Channel 6 (+)<br>Ground<br>Channel 0 (-)<br>Ground<br>Channel 2 (-)<br>Ground<br>Channel 4 (-)<br>Channel 6 (-) | 1 o<br>2 o<br>3 o<br>4 o | o 14<br>o 15<br>o 16<br>o 17<br>o 18<br>o 20<br>o 21<br>o 22<br>o 23<br>o 24<br>o 25<br>o 26 | Channel 0 (-)<br>Channel 2 (-)<br>Ground<br>Channel 4 (-)<br>Ground<br>N/C<br>Ground<br>N/C<br>Ground<br>N/C<br>Ground<br>N/C<br>Ground<br>N/C |

J1 Input Pin Definitions - Differential Mode

# 2.7 Single Ended Operation

The PCM-AIO allows eight single ended inputs with a voltage input range of 0 to 5 VDC for unipolar operation or -2.5 to +2.5 VDC for bipolar operation. An input channel is selected as a single ended input by setting the SI bit to a '0' when writing the channel select/command word.

# 2.8 Differential Operation

The PCM-AIO allows up to 4 channels of differential operation. Each differential channel requires two inputs, i.e. a (+) input and a (-) input. The PCM-AIO can have a mixture of single ended and differential input signals by programming the appropriate channel select/convert to each channel. A channel is programmed for differential operation by writing a '1' to the DI bit in the channel/convert word. For proper operation a channel that is used as a differential with differential inputs should have a bias return for each input, i.e. (+) and (-). A one megohm resistor from each differential input to ground will provide a sufficient bias return path for each input.

**Note:** It is possible to reverse the + and - differential inputs in software for a given channel. See Table 1 of the MAX180 datasheet on page 7-94 in Appendix C.

# 2.9 Unipolar/Bipolar Operation

Each channel on the PCM-AIO can be operated in either unipolar or bipolar mode. A unipolar input provides a 0 to 5 VDC input while a bipolar input provides a -2.5 VDC to + 2.5 VDC input. A channel is programmed for unipolar if the BP bit in the channel select/convert bit is set to '0' and by programming the BP bit to a '1', the channel is set for bipolar operation.

# 2.10 A/D Software Interface

An A/D conversion is started by writing a byte to the channel select/convert byte located at I/O port location BASE + 0. The actual location of the PCM-AIO depends on the I/O address that is selected by jumper block J8. The byte written to the channel select/convert port will set the PCM-AIO for the selected channel, unipolar/bipolar, and single ended/differential operation and then begin a conversion. It is important to note that in this mode of operation, the MAX180 allows only 1.875 uS to acquire the signal. If the input source impedance is greater than 8 kOhms, then the Asynchronous Hold mode will need to be used in order to allow enough time to acquire the signal. The PCM-AIO will convert the analog voltage to digital data in approximately 10 uS. If desired, an end of conversion interrupt can be generated on the PC/104 and routed through J7 as shown earlier. The interrupt controller will need to be initialized to take advantage of this feature. Another way to determine if the conversion is completed is to poll the ST status bit in the STATUS READ I/O port located at BASE + 4. The ST status bit is the most significant bit (MSB). The ST bit will be high '1' when the A/D convertor is BUSY and low '0' when it is finished. See the MAX180 datasheet, page 7-95, Figure 7b in the Appendix C for timing.

If the input source impedance is greater than 8 kOhms, the Track and Hold circuit will not have enough time to acquire the signal and the conversion will not be correct. Under these conditions, the MAX180 A/D convertor will need to operated in the "Asynchronous Hold Mode". See the MAX180 datasheet, page 7-98, Figure 10b in the Appendix C. The jumper J2 will need to be removed to place the MAX180 in the asynchronous mode. In the asynchronous mode it will be necessary to perform two write cycles to begin a conversion. The first write cycle is the same as before, except the channel data is written to an odd I/O port of BASE+1. This will select the proper channel and select the mode of operation, however a conversion will not begin until the second write cycle is generated by writing the same data to the I/O port BASE+0. This mode is made available so that a variable time can be inserted between write cycles to allow the Track/Hold circuit to acquire the input signal.

# 2.11 A/D CALIBRATION PROCEDURE

The PCM-AIO is calibrated at the factory for the 0-5V range of operation. When switching to another input range, a slight adjustment may be necessary. The following procedure is given to calibrate the PCM-AIO for any input range.

## 2.11.1 CALIBRATION PROCEDURE

1. Select the desired mode and input voltage range. Use a software routine that will loop continuously on one channel.

2. OFFSET/ZERO ADJUSTMENT. (TRIMPOT R3)

Apply a voltage source between the selected analog channel and ground. A 1uF ceramic capacitor should be used across the inputs to suppress noise. Adjust the output of the voltage source to + 1/2 LSB. Adjust the offset/zero trimming potentiometer R3 so that the output code flickers equally between 000 HEX and 001 HEX for unipolar operation and 800 HEX and 801 HEX for the bipolar mode.

3. FULL SCALE ADJUSTMENT. (TRIMPOT R2)

Change the output of the voltage source for + FS-1 1/2 LSB. Adjust the gain trimming potentiometer R2 so that the output code flickers equally between FFE HEX and FFF HEX.

# 2.12 **Output Coding**

| INPUT VOLTAGE RANGE                                       |                                                                          | CODING                                                                                                                     |

|-----------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                                                           | UNIPOLAR<br>0 TO +5V                                                     | STRAIGHT BINARY<br>MSB LSB                                                                                                 |

| +FS<br>+FS-1LSB<br>+1LSB<br>ZERO                          | 5.0000<br>4.9988<br>0.0012<br>0.0000<br>BIPOLAR<br>+/- 2.5V              | 1111 1111 1111<br>1111 1111 1110<br>0000 0000 0001<br>0000 0000 0000<br>OFFSET BINARY<br>MSB LSB                           |

| +FS<br>+FS-1<br>+1LSB<br>ZERO<br>-1LSB<br>-FS-1LSB<br>-FS | +2.5000<br>+2.4988<br>+0.0012<br>0.0000<br>-0.0012<br>-2.4988<br>-2.5000 | 0111 1111 1111<br>0111 1111 1110<br>0000 0000 0001<br>0000 0000 0000<br>1111 1111 1111<br>1000 0000 0001<br>1000 0000 0000 |

## 2.13 A/D SOFTWARE EXAMPLES

The following gives an example of an 8088/8086 assembly language routine that will interface to the PCM-AIO in synchronous polled mode for a 0 to 5 VDC, unipolar input range.

| mov dx,BASE_PORT | ;Set PC/104 Base I/O Address    |

|------------------|---------------------------------|

| mov al,0         | ;Chan 0, Single Ended, Unipolar |

| out dx,al        | ;Start Conversion               |

| add dx,4         | ;Point to Status Register       |

| in al,dx         | ;Read Status Bit                |

| test al,80H      | ;See if Conversion Finished     |

| jne wait         | ;If Not, Try Again              |

| mov dx,BASE_PORT | ;Point to Low data Byte         |

| in al,dx         | ;Read Low Data Byte             |

| mov bl,al        | ;Save Low Byte                  |

| inc dx           | ;Point to High Byte             |

| in al,dx         | ;Read High Byte                 |

| mov bh,al        | ;Combine with Low Byte          |

| and BX,0FFFH     | ;BX=Conversion Data             |

|                  |                                 |

The following program gives an example of a C program for performing A/D conversions with the PCM-AIO.

wait:

/\*

```

PCM-AIO

This program was written Primarily as a test/setup procedure

for the PCM-AIO board. (400-0172-000)

It also demonstrates how to access the MAX180 part,

and shows various methods of accessing the part.

Use getconv() for real-time readings in the foreground.

Use the Interrupt driven method to provide an array image

of all eight channels, constantly updated in the background.

Date: 05-22-1992.

Author: John Keller

Copyright 1992 by WinSystems. All Rights Reserved.

*/

#include <stdio.h>

#include <dos.h>

#include <stdlib.h>

#include <graph.h>

void ( interrupt far *OldTmr)(void);

/* Pointer to old ISR */

void ( interrupt far *TmrPtr)(void);

/* Temporary ISR Pointer */

void interrupt Int1c(void);

/* Declaration on ISR */

void ( interrupt far *OldRq5)(void);

/* Pointer to old ISR */

void (_interrupt _far *Rq5Ptr)(void);

/* Temporary ISR Pointer */

void interrupt Int0d(void);

/* Declaration on ISR */

unsigned int ticks[5],convi;

unsigned int tar[8] = \{0x000, 0x924, 0x249, 0xb6d, 0x492, 0xdb6, 0x6db, 0xfff\};

main()

{

int a,b,c;

for(a=0; a2;a++)

printf("

\n");

settextposition(1,1);

printf("Test for PCM-AIO boards\n");

printf("

To set up the board, connect the Voltage Source to the points\n");

printf(" indicated on the test fixture and set for 4.998 Volts.\n");

printf(" Adjust R3 on A/D until channel 0 %'Read%' is switching between 0 & 1.\n");

printf(" Next, Adjust R2 on A/D until channel 7 %'Read%' is FFE.\n");

printf(" Increase to 5.000 Volts. Ch 7 %'Read%' should now be FFF. Ch 0 %'Read%' should\n");

printf(" still be between 0 and 1.\n");

printf(" All channels should display PASS. You should NOT see the messages\n");

printf("%'Interrupt Failed%', or %'Busy is Stuck%' below the channels.\n");

OldRq5 = dos getvect(0x0d);

OldTmr = _dos_getvect(0x1c);

TmrPtr = Int1c;

Ra5Ptr = Int0d;

dos setvect(0x1c,TmrPtr);

```

```

_dos_setvect(0x0d,Rq5Ptr);

```

```

_displaycursor(_GCURSOROFF);

a = inp(0x21);

a &= 0xdf;

/*unmask irq5 */

outp(0x21,a);

_settextposition(11,10);

printf("Ch Trgt Read Difference");

while(1)

{

/* Scan all channels */

for(a=0; a; a++)

{

c=getconv(a,0);

/* Channel a, single ended, Unipolar */

_settextposition(a+12,10);

printf("%2d %3X %3X %3X",a,tar[a],c,abs(c-tar[a]));

if(c tar[a])

putch('-');

if(c tar[a])

putch('+');

if(c == tar[a])

putch('');

printf(" %3d%% ",abs(c-tar[a]) / 41);

if(a 0 && a )

{

/*1% resistors used for testing */

lf(abs(c-tar[a])()

printf("Pass");

else

printf("Fail");

if(a == 0 || a == 7)

{

lf(abs(c-tar[a]))

/*used for offset/gain calibration*/

printf("Pass");

else

printf("Fail");

}

if(kbhit())

break;

}

a = inp(0x21);

a |= 0x20;

/*mask irq5 */

outp(0x21,a);

_displaycursor(_GCURSORON);

_dos_setvect(0x0d,OldRq5);

dos setvect(0x1c,OldTmr);

}

/* Get conversion. */

/* MODE:

0

Single ended, Unipolar.

1

Single ended, Bipolar.

2

Differential, Unipolar.

3

Differential, Bipolar.

```

## NOTE:

```

In Differential mode, valid channels are still 0-7, however,

the channels are paired, evens with odds. (I.E. 0 with 1, 2 with 3,

etc.) The channel read becomes the "+" leg for the reading.

Example:

Channel 0 is 1.500 Volts lower than channel 1.

Mode is 2.

Channel read is 1.

Result: 1228(d) = 4CC(h).

If channel 0 had been read, the result would be zero.

*/

int getconv(int ch,int mode)

{

unsigned int a,b,c;

convi=0;

mode &= 3;

outp(0x100,ch|(mode<< 3));

ticks[0] = 2;

while(ticks[0] && (inp(0x104) & 0x80));

if(ticks[0] == 0)

{

settextposition(22,1);

printf("Busy is stuck.\n");

}

if(convi == 0)

{

settextposition(23,1);

printf("Interrupt Failed\n");

}

a = inp(0x100) \& 255;

b = inp(0x101) \& 15;

c = (b < 8) | a;

return(c);

}

/* Timer Tick Interrupt */

void interrupt Int1c(void)

{

int a;

for(a=0; a; a++)

{

if(ticks[a] 0)

ticks[a]—;

}

}

/* A2D Interrupt from PC/104 */

void interrupt Int0d(void)

{

/* Used by test. */

convi++;

```

```

/* SAMPLE APPLICATION */

/* Read All Eight Channels as Single/Uni & store in integer

Array variable results[8]. */

```

- /\* read & store the result.\*/

- /\* result[channel] = inp(0x100) | ((inp(0x101)&15)<8);\*/

```

/* Start next conversion */

```

```

/* ++channel &= 7;*/

```

```

/* outp(0x100,channel);*/

```

```

outp(0x20,0x20);

```

/\* Non-Specific EOI \*/

```

}

```

## 2.14 D/A Output Connector

|                                                                           | J                                                                                | 3                                                                                                                                                                                                                                                                                                                 |                                                                                                            |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| GND<br>N/C<br>N/C<br>GND<br>N/C<br>N/C<br>GND<br>N/C<br>GND<br>N/C<br>GND | 1 0<br>3 0<br>7 0<br>9 0<br>11 0<br>13 0<br>15 0<br>17 0<br>21 0<br>23 0<br>25 0 | <ul> <li>o</li> <li>2</li> <li>o</li> <li>4</li> <li>o</li> <li>6</li> <li>o</li> <li>8</li> <li>o</li> <li>10</li> <li>o</li> <li>12</li> <li>o</li> <li>14</li> <li>o</li> <li>16</li> <li>o</li> <li>18</li> <li>o</li> <li>20</li> <li>o</li> <li>22</li> <li>o</li> <li>24</li> <li>o</li> <li>26</li> </ul> | Channel 0<br>GND<br>N/C<br>Channel 1<br>GND<br>N/C<br>N/C<br>GND<br>N/C<br>GND<br>N/C<br>GND<br>N/C<br>GND |

The figure below defines the pins on the D/A output connector J3.

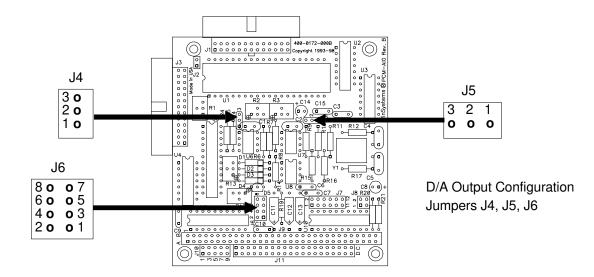

## 2.15 D/A Voltage Reference and Output Selection

Each of the D/A channels on the PCM-AIO can be jumpered for either a + 5VDC or - 5VDC reference and for either unipolar or bipolar operation. The following chart shows the appropriate jumper positions for these options.

|            | UNIPOLAR/BIPOLAR JUMPER SELECTION |                  |  |  |

|------------|-----------------------------------|------------------|--|--|

| RANGE      | CHANNEL 0                         | CHANNEL 1        |  |  |

| 0 to +5VDC | J6 3-4<br>J5 2-3                  | J6 7-8<br>J4 2-3 |  |  |

| -5V to +5V | J6 1-2<br>J5 1-2                  | J6 5-6<br>J4 1-2 |  |  |

WinSystems - "The Embedded Systems Authority"

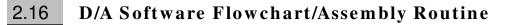

8088/8086 ASSEMBLY LANGUAGE ROUTINE

8088/8086 ASSEMBLY LANGUAGE ROUTINE

MOV DX,PORT\_ADDRESS MOV AL,LOW\_BYTE OUT DX,AL INC DX MOV AL,HIGH\_NIBBLE OUT DX,AL

NOTE: The LOW\_BYTE and HIGH\_NIBBLE form the 12 bit data that is written to the D/A. The PORT\_ADDRESS is the I/O address that is decoded on the selected PCM-AIO.

# 2.17 D/A CALIBRATION PROCEDURE

The D/A section of the PCM-AIO can be easily calibrated by the use of a digital voltmeter. To calibrate the D/A channels use the following procedure:

1. Install the board in the system and turn on the system to stabilize for at least 5 minutes.

- 2. Check the voltage reference output on J6 pin 1 for 5.000V. Adjust trimpot R13 if necessary.

- 3. Select the voltage reference output for each channel by the use of J6. See section 2.15.

- 4. For a unipolar output, output an 0FFF HEX to the channel or channels that are being calibrated and adjust the gain adjustment potentiometers for FS-1LSB as shown in the tables below.

5 .For a bipolar output, output an 0800 HEX to the channel or channels that are being calibrated and adjust the gain adjustment potentiometers for 0000 as shown in the tables below.

## VOLTAGE OUTPUT FOR UNIPOLAR AND BIPOLAR RANGES

| SCALE     | 0 to +5V | -5V to +5V |

|-----------|----------|------------|

| +FS-1 LSB | 4.9988   | 4.9976     |

| +1/2 FS   | 2.5000   | 0.0000     |

## GAIN ADJUSTMENT POTENTIOMETERS VERSUS CHANNELS

0 R1 1 R18

# APPENDIX A MAX180 DATASHEET REPRINT

## **General Description**

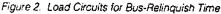

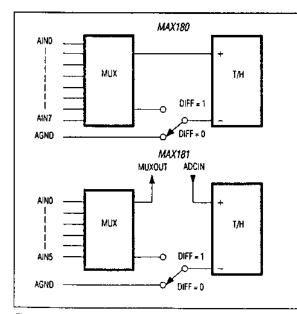

The MAX180/MAX181 are complete 12-bit Data Acquisition System (DAS) which combine 8/6-channel input multiplexer, high bandwidth Track-and-Hold (T/H), low-drift zener reference, and flexible microprocessor ( $\mu$ P) interface with high conversion speed and low power consumption. The MAX180/MAX181 can be configured by a  $\mu$ P for unipolar or bipolar conversions and single-ended or differential inputs. Both devices sample and digitize at 100kHz throughput rate and feature a fast 8- or 16-bit  $\mu$ P interface.

The MAX180 has 8 analog input channels, while the MAX181 has 6. The multiplexer output of the MAX180 is fed directly into the Analog-to-Digital Converter (ADC) input. The MAX181 brings out both the multiplexer output and ADC input to separate pins, allowing a programmable gain amplifier to be inserted between the MUX and the ADC.

The systems allow the user to choose between an internal or an external reference. Futhermore, the internal reference value and the offset can be adjusted, allowing the overall system gain and offset errors to be nulled. The multiplexer has high impedance inputs, simplifying analog drive requirements.

## **Applications**

High-Speed Servo Loops Digital-Signal Processing High-Accuracy Process Control Automatic Testing Systems

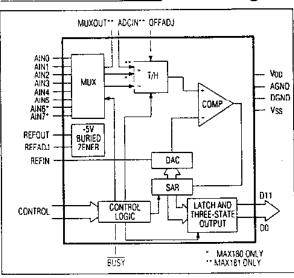

## Block Diagram

## \_\_\_ Features

- ♦ 12-Bit Resolution, ±1/2LSB Linearity

- 8-Channel Multiplexed inputs (MAX180)

- Single-Ended 1-of-6 Multiplexer (MAX181)

- Built-in Track-and-Hold

- 100kHz Sampling Rate

- DC and Dynamically Tested

- Internal 25ppm/'C Voltage Reference

- Each Channel Configurable for Unipolar (0V to +5V) or Bipolar (-2.5V to +2.5V) Input Range

- Each Channel Configurable for Single-Ended or Differential Inputs

- Fast 8-/16-Bit µP Interface

- +5V and -12V to -15V Supply Operation

- 110mW Power Consumption

# MAX180/MAX181

## **Ordering Information**

| PART       | TEMP. RANGE  | PIN-PACKAGE    | ERROR<br>(LSBs) |  |

|------------|--------------|----------------|-----------------|--|

| MAX180ACPL | 0°C to +70°C | 40 Plastic DIP | ±1/2            |  |

| MAX180BCPL | 0°C to +70°C | 40 Plastic DIP | ±1              |  |

| MAX180CCPL | 0°C to +70°C | 40 Plastic DIP | ±1              |  |

| MAX180ACOH | 0°C to +70°C | 44 PLCC        | ±1/2            |  |

| MAX1808CQH | 0'C to +70'C | 44 PLCC        | ±1              |  |

Ordering information continued on last page.

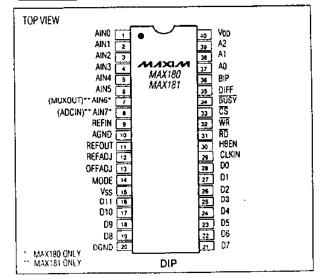

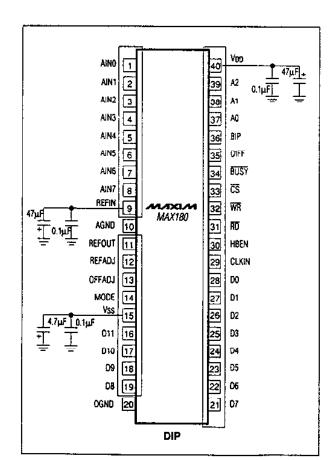

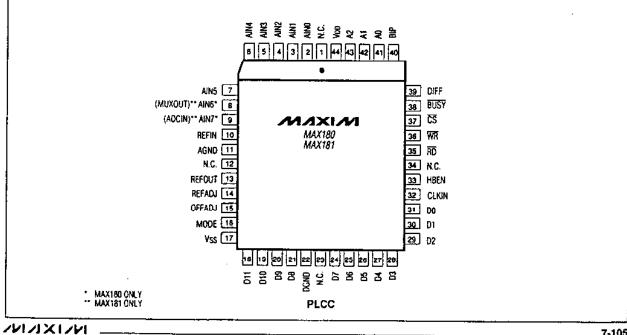

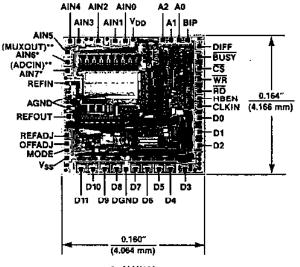

## Pin Configurations

Maxim Integrated Products 7-87

////XI/// is a registered trademark of Maxim Integrated Products.

1V171X17V1

## ABSOLUTE MAXIMUM RATINGS

| VDD to DGND         -0.3V, +7V           VSS to DGND         -0.3V, -17V           AGND to DGND         -0.3V, VDD + 0.3V | Continuous Power Dissipation (any package)<br>to +70°C |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| AIN _, MUXOUT, ADCIN, REFADJ,                                                                                             | Operating Temperature Ranges:                          |

| OFFADJ to REFIN                                                                                                           | MAX18_C 0'C to +70'C                                   |

| REFIN to DGND                                                                                                             | MAX18_E                                                |

| CS, WA, RD, CLK, A2-40.                                                                                                   | MAX18_MJL                                              |

| BIP, DIFF, HBEN to DGND -0.3V, VDD + 0.3V                                                                                 | Storage Temperature Range                              |

| BUSY, D0-D11 to DGND                                                                                                      | Lead Temperature (soldering, 10 sec)                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

$(V_{OD} = +5V \pm 5\%, V_{SS} = -12V \pm 5\% \text{ or } -15V \pm 5\%, \text{REFIN} = -5V.$  Internal Reference Mode, Bipolar Mode, Slow-Memory Mode (see text), ICLK = 1.6MHz external, MAX180/MAX181 all grades, TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.) (Note 1)

| PARAMETER                                             | SYMBOL            | CONDITIONS                                                                   | MIN   | ТҮР  | MAX        | UNITS  |

|-------------------------------------------------------|-------------------|------------------------------------------------------------------------------|-------|------|------------|--------|

| ACCURACY (Note 2)                                     |                   |                                                                              |       |      |            |        |

| Resolution                                            | N                 |                                                                              | 12    |      |            | Bits   |

| Integral Nonlinearity Error                           | INL               | MAX18_A<br>MAX18_B/C                                                         |       |      | ±1/2<br>±1 | LSB    |

| Differential Nonlinearity Error                       | DNL               | Guaranteed monotonic over temperature                                        | 1     |      | ±1         | LSB    |

| Unipolar Offset Error (Note 3)                        |                   |                                                                              | 1     | ±1   | ±4         | LSB    |

| Bipolar Offset Error (Note 3)                         |                   |                                                                              |       | ±1   | ±6         | LSB    |

| Unipolar Gain Error                                   |                   |                                                                              |       | ±2   | ±10        | LSB    |

| Bipolar Gain Errror                                   |                   |                                                                              |       | ±2   | ±15        | LSB    |

| Gain-Error Tempco (Note 4)                            |                   |                                                                              |       | ±5   |            | ррту/℃ |

| Channel-to-Channel Matching                           |                   |                                                                              |       | ±1/4 |            | LSB    |

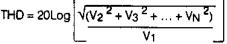

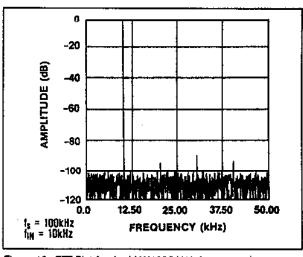

| DYNAMIC PERFORMANCE (No                               | te 2)             |                                                                              |       |      |            |        |

| Signal-to-Noise +<br>Distortion Ratio                 | SINAD             | 10kHz input signal, 100kHz sampling rate, bipolar mode, $T_A = +25^{\circ}C$ | 70    |      |            | dB     |

| Total Harmonic Distortion<br>(up to the 5th harmonic) | тно               | 10kHz input signal, 100kHz sampling rate,<br>bipolar mode, TA = +25°C        |       |      | -80        | dB     |

| Spurious-Free Dynamic Range                           | SFDR              | 10kHz input signal, 100kHz sampling rate,<br>bipolar mode, TA = +25°C        | 80    |      |            | dB     |

| Full-Power Sampling Bandwidth                         |                   | In track mode, under-sampled waveform                                        |       | 6    |            | MHz    |

| Track-and-Hold Acquisition<br>Time (Note 5)           | <sup>1</sup> ACQ  |                                                                              | 1.875 |      |            | μs     |

| _                                                     |                   | Asynchronous hold mode Note 5                                                | 7.500 |      | 8.125      |        |

| Conversion Time                                       | <sup>t</sup> CONV | ROM, Slow-Memory, and I/O Port Modes;<br>15-16 clock cycles                  | 9.375 |      | 10.000     | μs     |

| ANALOG INPUT                                          |                   |                                                                              |       |      |            |        |

| Voltage Range                                         |                   | AIN_, MUXOUT, and ADCIN                                                      | REFIN |      | Vod        |        |

| Unipolar, Single-Ended Range                          |                   | AIN_ to AGND                                                                 | 0     |      | 5.0        |        |

| Unipolar, Differential Range                          |                   | AIN_+ to AIN                                                                 | 0     |      | 5.0        | v      |

| Bipolar, Single-Ended Range                           |                   | AIN_ to AGND                                                                 | -2.5  |      | 2.5        |        |

| Bipolar, Differential Range                           |                   | AIN_+ 10 AIN                                                                 | -25   |      | 2.5        |        |

NINXIN

## ELECTRICAL CHARACTERISTICS (continued)

(VDD = +5V ±5%, VSS = -12V ±5% or -15V ±5%, REFIN = -5V, Internal Reference Mode, Bipolar Mode, Slow-Memory Mode (see text), fCLK = 1.6MHz external, MAX180/MAX181 all grades, TA = TMIN to TMAX, unless otherwise noted.) (Note 1)

| PARAMETER                                     | SYMBOL          | L CONDITIONS                                                                               |                              |       | ТҮР   | MAX   | UNITS   |

|-----------------------------------------------|-----------------|--------------------------------------------------------------------------------------------|------------------------------|-------|-------|-------|---------|

| ANALOG INPUT (continued)                      |                 |                                                                                            |                              |       |       |       |         |

| locut Current                                 |                 | AIN_ ,                                                                                     | MAX 180                      |       |       | ±1.0  |         |

| Input Current                                 |                 | ADCIN,                                                                                     | MAX181                       |       |       | ±0.1  | μA      |

| Mux-On Resistance                             | Ron             | AIN_ = 2.5V, IMUXOUT = 1.2                                                                 | 5mA, MAX181                  |       |       | 2     | kΩ      |

| Mux-On Leakage Current                        | 1 <sub>ON</sub> | $AIN_ = MUXOUT = \pm 5V$                                                                   | MAX181                       |       |       | ±100  | nΑ      |

| Mux-Off Leakage Current                       | IN (OFF)        | $AIN_ = \pm 5V$ , $V_{OUT} = \pm 5V$ ,                                                     | MAX181                       |       |       | ±100  | пA      |

|                                               | IOUT (OFF)      | $AIN_ = \pm 5V$ , $V_{OUT} = \pm 5V$ ,                                                     | MAX181                       |       |       | ±100  |         |

| Input Capacitance (Note 5)                    | Cin             | AIN_, ADCIN                                                                                |                              |       | 25    | 35    | ρF      |

| input capacitance (NOIE 5)                    | CIN             | MUXOUT                                                                                     |                              |       | 35    | 45    | P.      |

| REFERENCE INPUT                               |                 |                                                                                            |                              |       |       |       |         |

| Input Range (Note 5)                          |                 |                                                                                            |                              | -4.92 | -5.00 | -5.08 | V       |

| Input Current                                 |                 |                                                                                            |                              | • •   |       | -2    | mA      |

| Input Resistance                              |                 |                                                                                            |                              | 2.5   |       |       | kΩ      |

| REFERENCE OUTPUT                              |                 |                                                                                            |                              |       |       |       |         |

| VREF Output Voltage                           |                 | T <sub>A</sub> = +25°C                                                                     |                              | -4.98 | -5.00 | -5.02 | V       |

| VREF Output Tempco (Note 6)                   |                 | MAX18_A/B                                                                                  |                              |       |       | 25    | acont C |

|                                               |                 | MAX18_C                                                                                    |                              |       |       | 45    | ppm/*C  |

| VREF Load Regulation (Note 7)                 |                 | OUT = 0mA to 5mA, TA = +                                                                   |                              | 0.2   | 1.0   | mV/mA |         |

| REFADJ, OFFADJ                                |                 |                                                                                            |                              |       |       |       | ·       |

| Input Current                                 |                 | VREFADJ, VOFFADJ = VDD to REFIN                                                            |                              |       |       | ±1    | μA      |

| Disable Threshold                             |                 |                                                                                            |                              | 4.5   |       |       | V       |

| REFADJ Adjustment Range                       |                 | REFIN < REFADJ <agnd< td=""><td></td><td>±60</td><td>±80</td><td></td><td>mV</td></agnd<>  |                              | ±60   | ±80   |       | mV      |

| OFFADJ Adjustment Range                       |                 | REFIN < OFFADJ <agnd< td=""><td></td><td>±15</td><td>±25</td><td></td><td>LS8</td></agnd<> |                              | ±15   | ±25   |       | LS8     |

| LOGIC INPUTS                                  |                 |                                                                                            |                              |       |       |       |         |

| Input Low Voltage                             | N/II            | MODE                                                                                       |                              |       |       | 0.5   | V V     |

|                                               | ViL             | CS, RD, WR, CLK, A2-A0, D                                                                  | IFF, BIP, HBEN               |       |       | 0.8   | *       |

| Input High Veltage                            | Nex             | MODE                                                                                       |                              | 4.5   |       |       |         |

| Input High Voltage                            | ViH             | CS, RD, WR, CLK, A2-A0, D                                                                  | IFF, BIP, HBEN               | 2.4   |       |       |         |

| Input Mid-Level Voltage                       | VMID            | MODE                                                                                       |                              | 1.5   |       | 3.5   | V       |

| Input Floating Voltage                        | VELT            | MODE                                                                                       |                              |       | 2.5   |       | V       |

|                                               |                 | MODE                                                                                       | T <sub>A</sub> = +25°C       |       | ±50   | ±100  |         |

| Input Current                                 | Jin             | MUUE                                                                                       | $T_A = T_{MIN}$ to $T_{MAX}$ |       | ±50   | ±100  | μA      |

|                                               |                 | CS, RD, WR, CLK, A2-A0,                                                                    | T <sub>A</sub> = +25°C       |       |       | ±1    |         |

|                                               | DIFF. BIP.      |                                                                                            | TA = TMIN to TMAX            |       |       | ±10   |         |

| Input Capacitance (Note 5)                    | CiN             |                                                                                            |                              |       |       | 15    | ρF      |

| LOGIC OUTPUTS                                 |                 |                                                                                            |                              |       |       |       |         |

| Output Low Voltage                            | Vol             | D11-D0, BUSY, RDY, ISINK                                                                   | = 1.6mA                      |       |       | 0.4   | V       |

| Output High Voltage                           | VOH             | D11-D0, BUSY, RDY, ISOUR                                                                   |                              | 4.0   |       |       | V       |

| Floating State Leakage Current                | ILKG            | D11-D0, VOUT = 0V to VDD                                                                   |                              |       |       | ±10   | μA      |

| Floating State Output<br>Capacitance (Note 5) | Cout            |                                                                                            |                              | ••    |       | 15    | pF      |

MAX180/MAX181

1V1/X1/VI

7-89

## ELECTRICAL CHARACTERISTICS (continued)

(VDD = +5V ±5%, Vss = -12V +5% or -15V +5%, REFIN = -5V, Internal Reference Mode, Bipolar Mode, Slow-Memory Mode (see text), fCLK = 1.6MHz external, MAX180/MAX181 all grades, TA = TMIN to TMAX, unless otherwise noted.) (Note 1)

| PARAMETER                                          | SYMBOL | CONDITIONS                                           | MIN    | TYP  | MAX    | UNITS |

|----------------------------------------------------|--------|------------------------------------------------------|--------|------|--------|-------|

| POWER REQUIREMENTS                                 |        |                                                      |        |      | 10.04  | 0.010 |

| Supply Voltage (Note 1)                            | COV    |                                                      | 4.75   | 5.00 | 5.25   |       |

|                                                    | Vss    |                                                      | -11.40 |      | -15.75 | l v   |

| Supply Current                                     | 100    | V <sub>DD</sub> = 5V                                 |        | 4.5  | 7.0    | -     |

|                                                    | Iss    | $V_{SS} = -12V$                                      |        | 7.0  | 10.0   | MA    |

| Power Dissipation                                  | PD     | $V_{DD} = 5V, VSS = -15V$                            |        | 110  | 155    | mW    |

|                                                    |        | Input near FS, Vss = -12V,<br>Vpp = 4.75V to 5.25V   |        | ±1/2 | ±1     |       |

| Power-Supply Rejection,<br>with Internal Reference | PSR    | Input near FS, VDD = 5V,<br>VSS = -14.25V to -15.75V |        | ±1/8 | ±1/2   | LSB   |

|                                                    |        | Input near FS, Vpp = 5V,<br>VSS = -11.4V to = -12.6V |        | ±1/8 | ±1/2   |       |

## TIMING CHARACTERISTICS

(VDD = +5V, VSS = -12V, folk = 1.6MHz, Internal Reference Mode, TA = TMM to TMAX, unless otherwise noted.) (Note 8)

| PARAMETER                   | SYMBOL | COND                                  | ITIONS                                | i - | = +2:  |     | 1   | X18_C/6 |               | AX18 |     | UNITS    |

|-----------------------------|--------|---------------------------------------|---------------------------------------|-----|--------|-----|-----|---------|---------------|------|-----|----------|

| CS to RD Setup time         | t 1    | :<br>                                 | Note 5                                |     |        | MAX |     | TYP M   |               | TYP  | MAX |          |

| CS to RD Hold time          | t2     |                                       |                                       | 0   | -      |     | 0   |         |               |      |     | ns<br>ns |

| CS to WR Setup time         | t3     | ··-·                                  |                                       | 0   |        | •   | Ō   |         | -+            |      |     | 05       |

| CS to WR Hold time          | t4     | · · · · · · · · · · · · · · · · · · · | Note 5                                | 0   |        |     | 0   |         |               |      |     | ns       |

| WR Low Pulse Width          | ts     |                                       |                                       | 120 |        |     | 120 |         | 120           |      |     | <br>     |

| WR High Pulse Width         | 16     | MODE = 0<br>or 1                      | Note 5                                | 200 |        |     | 200 | _       | 200           |      |     | ns       |

| DATA IN to WR Setup Time    | t7     |                                       |                                       | 80  |        |     | 100 |         | 120           |      |     | ns       |

| DATA IN to WR Hold Time     | tø     |                                       |                                       | 0   |        |     | 0   |         | 0             |      |     | ns       |

| WR Rising to BUSY Delay     | 19     | CL = 50pF, N                          | MODE = 1                              |     |        | 160 |     | 18      | 30            |      | 200 | ns       |

| WR Falling to BUSY Delay    | t10    |                                       | /ODE = open                           | i   |        | 220 |     |         | 30            |      | 280 | 05       |

| RD Low Pulse Width          | t11    |                                       |                                       | 100 |        |     | 130 |         | 150           |      | 200 | ns       |

| RD High Pulse Width         | t12    |                                       | Note 5                                | 200 |        |     | 200 |         | 200           | ·    |     | ns       |

| DATA IN to RD Setup Time    | t13    |                                       |                                       | 80  |        |     | 100 |         | 120           |      |     |          |

| DATA IN to RD Hold Time     | t14    |                                       | _                                     | 0   | •••••• |     | 0   |         | 10            |      |     |          |

| RD to BUSY Fall Delay       | t15    | Ըլ = 50pF                             |                                       |     |        | 150 |     | 17      |               |      | 200 |          |

| RD to Data out Valid        | t16    | CL = 100pF                            | Note 9                                |     | 50     | 100 |     | 13      |               |      | 150 | ns       |

| RD to Data out Three-State  | t17    |                                       | Notes 9, 10                           |     | 30     | 50  |     |         | -             |      | 75  | ns       |

| HBEN to RD or WR Setup Time | t18    |                                       | · · · · · · · · · · · · · · · · · · · | 80  |        |     | 100 |         | 120           |      |     |          |

| HBEN to RD or WR Hold Time  | 119    |                                       |                                       | 0   | ·      |     | 0   |         | 0             |      |     |          |

| CS to READY Fail Delay      | t20    | Ci = 50pF                             |                                       |     |        | 110 |     | 13      | - <del></del> |      | 150 | ns       |

## TIMING CHARACTERISTICS (continued)

(VDD = +5V, VSS = -12V, fCLK = 1.6MHz, internal Reference Mode, TA = TMIN to TMAX, unless otherwise noted.) (Note 8)

| PARAMETER                                                     | SYMBOL | COND             | CONDITIONS |     | TA = +25°C |     | MAX18_C/E |     | MAX18_M |     |     |     |          |

|---------------------------------------------------------------|--------|------------------|------------|-----|------------|-----|-----------|-----|---------|-----|-----|-----|----------|

| <u></u>                                                       |        | ·                |            | MIN | TYP        | MAX | MIN       | TYP | MAX     | MIN | TYP | MAX | UNITS    |

| BUSY to Data Out Valid                                        | 121    | $C_{L} = 100 pF$ | Note 9     |     |            | 125 |           |     | 150     |     |     | 170 | ns       |

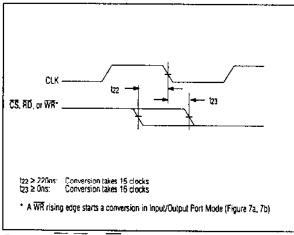

| CS, RD, or WR to CLK<br>Setup time for 15 clock<br>conversion | t22    |                  | Note 5     | 220 |            |     | 220       |     |         | 220 |     |     | ns<br>ns |

| CS, RD, or WR to CLK<br>Setup time for 16 clock<br>conversion | 123    |                  | Note 5     | 0   |            |     | 0         |     |         | 0   |     |     | n\$      |

**Note 1:** Performance at power-supply tolerance limits guaranteed by power-supply rejection test. **Note 2:** VDD = +5V, VSS = -15V, FS = +5V, REFIN = -5V, **Note 3:** Typical change over temperature is ±1LSB. **Note 4:** FS Tempco =  $\Delta$ FS/ $\Delta$ T, where  $\Delta$ FS is full-scale change from TA = +25°C to TMIN or to TMAX.

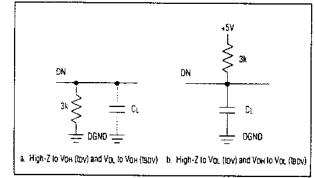

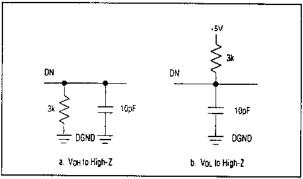

Note 4: FS Tempco =  $\Delta$ FS/ $\Delta$ T, where  $\Delta$ FS is full-scale change from TA = +25 C to TMIN or to TMAX. Note 5: Guaranteed by design Note 6: REFIN TC =  $\Delta$ REFIN/ $\Delta$ T, where  $\Delta$ REFIN is reference voltage change from TA = +25°C to TMIN or to TMAX. Note 7: Load current should remain constant during conversion. This current is in addition to the DAC input current. Note 8: All inputs are OV to +5V swing with tr = tr = 5ns (10% to 90% of 5V) and timed from a voltage level of +1.6V. Note 9: the and tg1 are measured with the load circuits of Figure 1 and defined as the time required for an output to cross 0.8V or 2.4V. Note 10: t<sub>17</sub> is defined as the time required for the data lines to change 0.5V when the circuit load is as shown in Figure 2.

|   | Pin | Descriptio | 2 |

|---|-----|------------|---|

| - |     | rescriptio |   |

| NAME          | M/    | AX180          | M/    | AX181       |                                                                           |

|---------------|-------|----------------|-------|-------------|---------------------------------------------------------------------------|

|               | DIP   | PLCC           | DIP   | PLCC        | FUNCTION                                                                  |

| AIN0-AIN5     | 1+6   | 2-7            | 1-6   | 2-7         | Analog Inputs to the mux: 0V to +5V unipolar, -2.5V to +2.5V bipolar      |

| AIN6-AIN7     | 7,8   | 8,9            |       |             | Analog Inputs to the mux: 0V to +5V unipolar, -2.5V to +2.5V bipolar      |

| MUXOUT        |       |                | 7     | 8           | Muliplexer Output                                                         |

| ADCIN         | ļ,    |                | 8     | 9           | Analog Input to track-and-hold                                            |

| REFIN         | 9     | 10             | 9     | 10          | Reference Input                                                           |

| AGND          | 10    | 11             | 10    | 11          | Analog Ground                                                             |

| REFOUT        | 11    | 13             | 11    | 13          | -5V Reference Output                                                      |

| REFADJ        | 12    | 14             | 12    | 14          | -5V Heterence Adjust. Connect to Vop if not required.                     |

| OFFADJ        | 13    | 15             | 13    | 15          | Offset Adjust. Connect to Vpp if not required.                            |

| MODE          | 14    | 16             | 14    | 16          | Interface Mode Select pin.                                                |

| Vss           | 15    | 17             | 15    | 17          | Negative Supply: -15V or -12V                                             |

| <u>D11-D8</u> | 16-19 | 18-21          | 16-19 | 18-21       | Three-State Data Outputs, MSB = D11                                       |

| DGND          | 20    | 22             | _20   | 22          | Digital Ground                                                            |

| D7-00         | 21-28 | 24-31          | 21-28 | 24-31       | Three-State Data Outputs, LSB = D0                                        |

|               | 29    | 32             | 29    | 32          | Clock Input, TTL/CMOS compatible                                          |

| HBEN          | 30    | 33             | _ 30  | 33          | High-Byte Enable Input                                                    |

| <u>RD</u>     | 31    | 35             | 31    | 35          | READ Input                                                                |

| <u>WR</u>     | 32    | 36             | 32    | 36          | WRITE Input (MODE = 1 or Open) READY Output (MODE = 0)                    |

| <u>ČS</u>     | 33    | 37             | _33   | 37          | CHIP-SELECT Input                                                         |

| BUST          | 34    | 38             | 34    | 38          | BUSY Output                                                               |

| DIFF          | 35    | 39             | 35    | 39          | Single-Ended Mode: DIFF = 0, Differential Mode: DIFF = 1                  |

| BIP           | 36    | 40             | 36    | 40          | Unipolar Mode: BIP = 0, Bipolar Mode: BIP = 1                             |

| A0-A2         | 37-39 | 41-43          | 37-39 | 41-43       | Multiplexer Channel Address Input: A2 = MSB, A0 = LSB                     |

| VDD           | 40    | 44             | 40    | 44          | Positive Supply: +5V Input (substrate conflected to VDD)                  |

| N.C.          |       | 1,12,<br>23,34 |       | 1,12, 23,34 | No Connect. No internal connection. Leave pin open or<br>connect to AGND. |

MAXIM

7-91

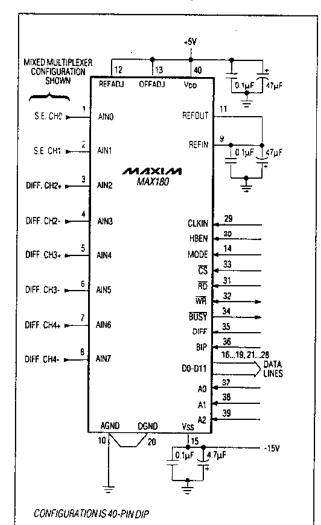

Figure 1. Load Circuits for Access Time

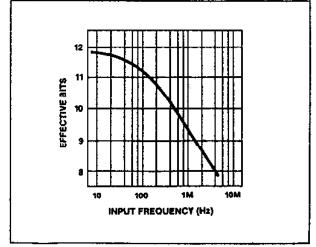

## A/D Converter Operation

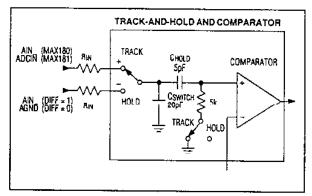

The MAX180/MAX181 use successive approximation and input track-and-hold (T/H) circuitry to convert an analog signal to a series of 12-bit digital output codes. The control logic interfaces easily to uPs, requiring only a few passive components for most applications. The T/H does not require an external capacitor. Figure 3 shows the MAX180 typical operating circuit.

#### Starting a Conversion

Regardless of the mode or interface selected, the following sequence occurs once conversion is started:

- The data inputs that configure the data-acquisition system (DAS) latch, and the interface signals the μP that a conversion has started.

- The mux directs the selected input signal to the T/H input.

- 3. A fixed time delay allows the T/H to acquire the signal. In all modes except asynchronous hold, this delay is 3 clock cycles. In asynchronous hold, the  $\mu$ P controls this delay.

- The T/H switches to hold mode. The T/H output delivers a stable, single-ended sample of the input signal to the A/D input.

- The successive approximation cycle begins. The ADC tests and sets each of the 12 bits in turn, from most to least significant. Bit decisions occur on the CLKIN falling edges, for a total of 12 clock cycles.

- Output data is latched by the output registers, and the interface signals the μP that conversion is complete and data is available.

Figure 3. MAX180 Typical Operating Circuit

\_ /VI/IXI/VI

## Analog Input - Track-and-Hold

Figure 4 shows the equivalent input circuit, illustrating the sampling architecture of the ADC's analog comparator. The input capacitance acts as the hold capacitor and is charged by the input signal with every A/D conversion. The capacitance is charged through an internal  $1k\Omega$  resistor in series with the input. Note: Figure 4's switches represents both the mux and hold switches.

Figure 4 Equivalent Input Circuit

When in single-ended input mode and between conversions (BUSY = High), the selected analog input is connected to the hold capacitor (track mode). When a conversion starts, CHOLD disconnects from the + T/H input, thus sampling the input (see 'Digital Interface' section for percise T/H timing). When the switch closes at conversion end, CHOLD reconnects to the input and charges to the input signal. The loading effect of the analog inputs on the signal is such that a high-speed input buffer is usually NOT needed because the ADC disconnects from the input during the actual conversion.

The previous explanation applies for the differential input mode if "input" is replaced by AIN+ and "analog ground" is replaced by AIN-. In the differential input mode, A0-A2 select the input channel pairs (Table 1). Only the signal side of the input channel is held by the T/H; the return side must remain stable within  $\pm 0.5LSB (\pm 0.1LSB$  for best results) during the conversion. For example, a commonmode signal of 0.33Vp-p at 60Hz results in a maximum error of 0.5LSB.

The T/H starts tracking when the ADC is deselected (BUSY = High). Hold mode begins 3 clock cycles after a conversion is initiated in all but the Asynchronous Hold Mode. Variation in hold-mode delay from one conversion to the next (aperture jitter) is less than 100ps. Figures 7-11 detail the T/H and interface timing for the various interface modes.

/M/IXI/M ---

The time required for the T/H to acquire an input signal is a function of how quickly the input capacitance is charged. If the input source impedance is high, the acquisition time lengthens and more time must be allowed between conversions. Acquisition time is calculated by:

tACQ = 10(Rs + Rin)20pF (but never less than 1.875us)

where  $R_{IN} = 1k\Omega$ , and  $R_S =$  source impedance of the input signal.

## Input Bandwidth

The A/D's input tracking circuitry is excellent for tracking large signals and wide bandwidths and does not exhibit the slew-rate limitations of many other ADC T/Hs. The MAX180/MAX181 T/H's full-power bandwidth is typically 6MHz; this allows the measurement of periodic signals with bandwidths exceeding the ADC's sample rate (100kHz) using under-sampling techniques. Important note: If under-sampling is used to measure high-frequency signals, take special care to avoid aliasing errors. Without adequate input filtering, high-frequency noise could be aliased into the measurement band.

#### Reference

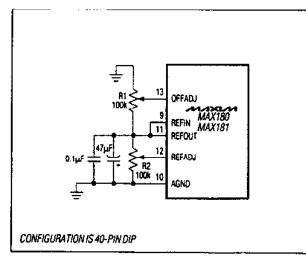

The MAX180/MAX181 operate with either the internal reference or an external -5V reference. In both cases, REFIN must be bypassed to AGND with a  $47\mu$ F electrolytic capacitor in parallel with a  $0.1\mu$ F ceramic capacitor to minimize noise and maintain a low impedance at high frequencies. REFIN is connected directly to the internal DAC, and the current load varies between 0mA and 1mA during conversion.

#### Internal Reference

The internal reference is buffered through an amplifier whose output connects to REFOUT. To operate the MAX180/MAX181 with the internal reference, connect REFIN to REFOUT. Do not connect a resistor between the bypass capacitors and REFIN. The reference buffer amplifier can sink 5mA for external loads. Adjust the reference output at REFADJ (Figure 14).

#### External Reference

With a -5V external reference, bypass REFIN to AGND with a 47 $\mu$ F electrolytic capacitor in parallel with a 0.1 $\mu$ F ceramic capacitor. The reference source impedance must be less than 0.2 $\Omega$  and must be able to sink the internal DAC load of 1mA. Connect REFOUT to Vss and REFADJ to VDD to prevent noise. If REFIN is driven above AGND during power sequencing, latchup can occur. Connect a Schottky clamp diode (IN5817) to prevent REFIN from substantially exceeding AGND.

## Table 1. Address vs. Channel Selection (see Figure 4)

MAX180/MAX181

|               | A2 | A1 | AO | SE/DIFF | AINO | AIN1     | AIN2                     | AIN3   | AIN4    | AIN5 | AIN6 | AIN7 | COM |

|---------------|----|----|----|---------|------|----------|--------------------------|--------|---------|------|------|------|-----|

| MAX180/MAX181 | 0  | 0  | 0  | 0       | +    |          |                          | 1      |         |      |      |      | _   |

| MAX180/MAX181 | 0  | 0  | 1  | 0       |      | +        |                          |        |         | 1    |      |      | _   |

| MAX180/MAX181 | 0  | 1  | 0  | 0       |      |          | +                        |        |         |      |      |      | -   |

| MAX180/MAX181 | 0  | 1  | 1  | 0       |      |          |                          | +      |         |      |      |      | -   |

| MAX180/MAX181 | 1  | 0  | 0  | 0       |      |          |                          |        | +       |      |      |      | -   |

| MAX180/MAX181 | ٦  | 0  | 1  | 0       |      | i        |                          |        |         | +    |      |      | -   |

| MAX180        | 1  | 1  | 0  | 0       |      | ]        |                          |        |         |      | +    |      | -   |

| MAX181        | 1  | 1  | 0  | 0       |      | M        | MUXOUT CONNECTED TO AGND |        |         |      |      |      | +,- |

| MAX180        | 1  | 1  | 1  | 0       |      | <u> </u> |                          |        |         |      |      | +    |     |

| MAX181        | 1  | 1  | 1  | 0       |      | C C      | H 0-5, Al                |        | OUT ARE | OPEN |      |      | -   |

| MAX180/MAX181 | 0  | 0  | 0  | 1       | +    | -        |                          |        |         |      |      |      |     |

| MAX180/MAX181 | 0  | 0  | 1  | 1       | -    | +        |                          |        |         |      |      |      |     |

| MAX180/MAX181 | 0  | 1  | 0  | 1       |      |          | +                        | -      |         |      |      | 1    |     |

| MAX180/MAX181 | 0  | 1  | 1  | 1       |      |          | -                        | +      |         |      | i    |      |     |

| MAX180/MAX181 | 1  | 0  | 0  | 1       |      |          |                          |        | +       | -    |      |      |     |

| MAX180/MAX181 | 1  | 0  | 1  | 1       |      |          |                          |        | -       | +    |      |      |     |

| MAX180        | 1  | 1  | 0  | 1       |      |          |                          | 1      |         |      | +    | -    |     |

| MAX180        | 1  | 1  | 1  | 1       |      |          |                          |        |         |      | _    | +    |     |

| MAX181        | 1  | 1  | 0  | 1       |      | N N      | UXOUT                    | CONNEC | TED TO  | AGND |      | 1    | +,- |

| MAX181        | 1  | 1  | 1  | 1       |      | C        | H 0-5, AI                |        | OUT ARE | OPEN |      |      | -   |

Figure 5. Multiplexer channel configuration

7-94

Figure 6. Input/Output Port Mode (12-Bit-Wide Data Bus Shown)

1/1/X1/VI

\_\_\_\_\_

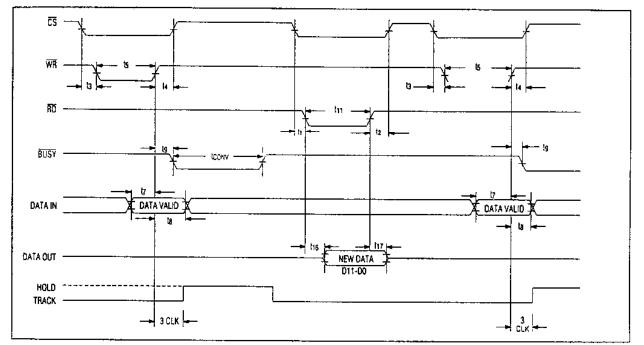

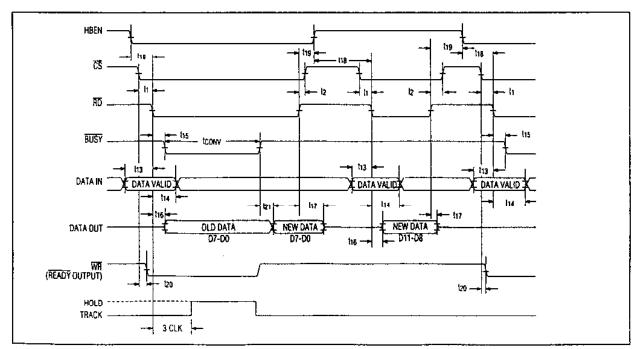

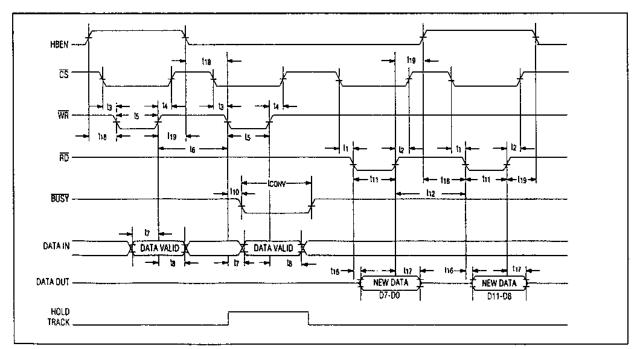

Figure 7a. Input/Output Port-Mode timing, parallel read (MODE = 1, HBEN = 0).

Figure 7b. Input/Output Port-Mode timing, two-byte read (MODE = 1).

MUXINI -

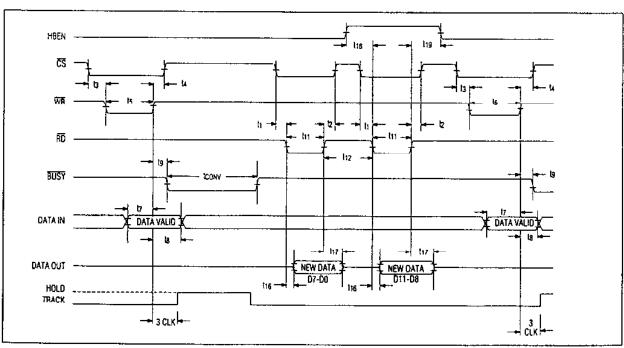

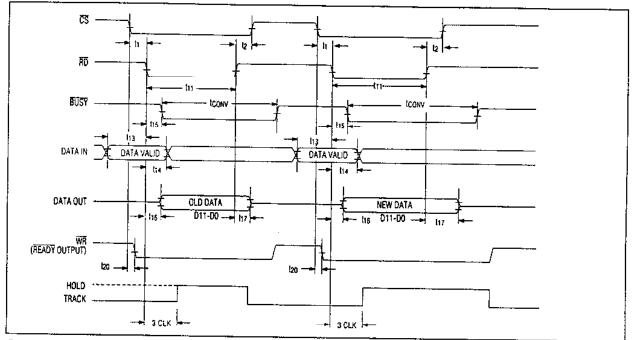

Figure 8a. Slow Memory Mode timing, parallel read (MODE = 0, HBEN = 0).

Figure 8b. Slow Memory Mode timing, two-byte read (MODE = 0).

WINXINI

7-96

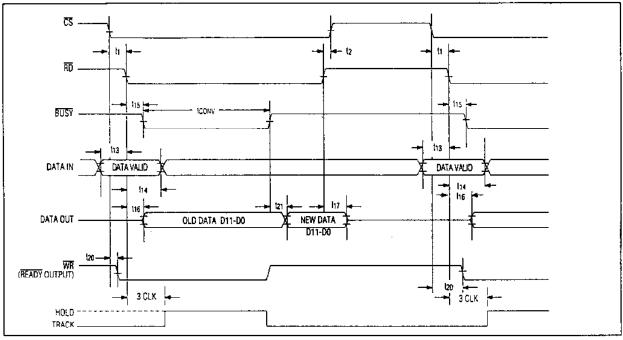

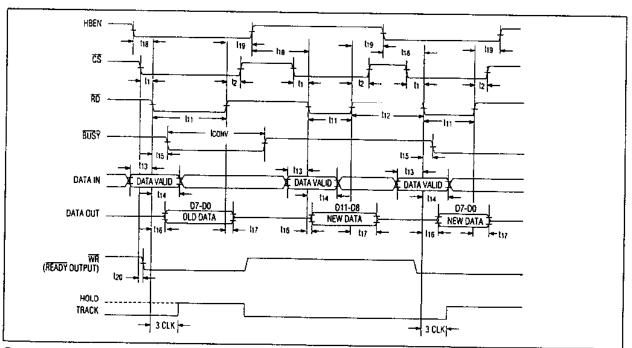

Figure 9a. ROM Mode timing, parallel read (MODE = 0, HBEN = 0).

Figure 9b. ROM Mode timing, two-byte read (MODE = 0).

NUNXINI.

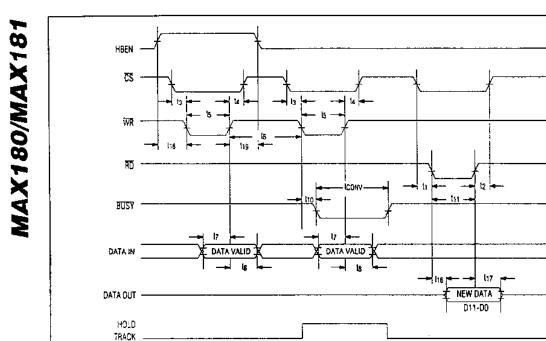

Figure 10b. Asynchronous Hold Mode timing, two-byte read (MODE = open circuit)

MINXIM

Figure 11. CS, RD, or WR to CLK Setup and Hold Time for Synchronous Operation

# \_\_\_\_\_Digital Interface Input/Output Port Mode (MODE = 1)

In this mode, data inputs and outputs are usually connected together (Figure 6), and the µP writes the configuration data to the DAS internal register with a write instruction (Figure 7). This starts a conversion, as indicated by the high-to-low transition of BUSY. The mux connects the selected input channel to the T/H, which acquires the signal during the first 3 clock cycles. On the falling edge of the 3rd clock, the T/H switches to hold mode, and the A/D conversion starts. 15 clock cycles after WR goes high, BUSY goes high, and the conversion result latches into three-state output buffers. The µP can then access the conversion result with a read instruction. For 16-bit bus operation, HBEN = 0, and the 12-bit result is read directly. For 8-bit bus operation, HBEN = 0 during the conversion, and the read instruction returns the 8 LSBs. A second read with HBEN = 1 returns the 4 MSBs in the low nibble. Note: In any mode, HBEN = 1 disables conversion start.

The DAS internal register is 5 bits wide: 3 bits for the analogchannel address, 1 bit for single-ended/differential mux operation, and 1 bit for unipolar/bipolar A/D operation.

## Slow Memory Mode (MODE = 0)

The DAS appears to the  $\mu$ P as memory or as a slow peripheral in memory mode. The 5 configuration bits can be preset by an external data latch, a decoded device address, or any external selection logic. A

# Complete, 8-Channel, 12-Bit Data-Acquisition Systems

read instruction initiates a conversion as shown in Figure 8. In this mode, the WR input functions as the RDY output and goes low when CS goes low. BUSY goes low after RD goes low, indicating the beginning of a signal acquisition cycle, and can be used to place the  $\mu$ P into a wait state. When the conversion is complete, BUSY releases the  $\mu$ P from its wait state. The  $\mu$ P can then access the conversion result with a read instruction. For 16-bit bus operation, HBEN = 0, and the 12-bit result is read directly. For 8-bit bus operation, HBEN = 0 during the conversion, and the read instruction returns the 8 LSBs. A second read with HBEN = 1 returns the 4 MSBs in the low nibble. Note: In any mode, HBEN = 1 disables conversion start.

## ROM Mode, Parallel Read (MODE = 0)